4558

State of Art, Powerful, System On Chip, Design,Development and Implementation of Multi Channel Transceiver for MRI Spectrometer1Medical Systems Division, S.A.M.E.E.R. Mumbai, Mumbai, India

Synopsis

Keywords: New Devices, Spectroscopy, System -on-chip,MIMO Based smart MRI Spectrometer

The increasing complexity of modern MRI hardware design makes system challenging. MRI systems equipped with multi-channel exciter and multi-channel data-acquisition modules, particularly high-channel-counts often requires a huge cost. This abstract summaries the design and development of a low cost, small form factor, system on chip approach to realize a complete 1.5 T MRI spectrometer on a small chip of 28 nanometer fabric. The developed system executes parallel image processing algorithms and compatible instrumentation for accurate spatial and temporal requirements.Introduction

The demand for developing a complete customized and reconfigurable embedded spectrometer for Magnetic Resonance Imaging with power of on chip data acquisition, processing and image reconstruction has been the need of the recent times [1]. This abstract summaries succinctly the design and development of a successfully integrated state of art but extremely powerful, ‘System on chip’, 1.5 T MRI spectrometer with a customized clinical user interface to generate human anatomical pulse excitation systems of any shape, of any width with very high precision time of nanoseconds accuracy. These waveforms are developed for not only multi-slice applications of Larmor frequency signals but also for gradient signals too. The power of parallel computing with multi-thread on chip processor layers have been exploited to develop some high speed On-chip image reconstruction algorithms of even sub Nyquist model [2]. which saves huge time in clinical applications as compared to the conventional available MRI systems. Field Programmable Gate Arrays (FPGAs) are used by exploiting the reconfigurable resources and implementing the complicated image processing algorithms at very fast speeds in real time in parallel and pipelined fashion using HDL languages for customized MRI spectrometer.Method

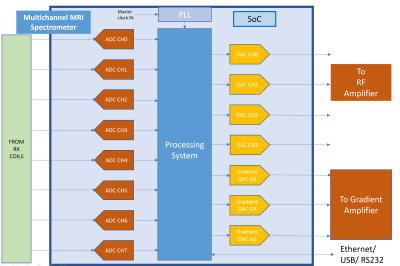

Speed of MR imaging is primarily determined by the speed and time elapsed by the system to acquire, process and generate the clinical image. In this approach, the accelerators with desired computing core are interfaced directly to the programmable RTL logic layers. [3][4]. This type of coupled togetherness of logic and processor layer accelerators exposes no communication overhead and offers quick synchronization, processing and transforms of data to spatial domain outputs for evaluation to clinicians and medical fraternity. A 28 nanometer fabric which include dual ARM cortex processors and programmable electronic logic array is customized and implemented for MRI spectrometer [5][6]. The implementation of 1.5 T MRI spectrometer is as shown in figure1. The implemented design generates Multiple RF output and captures multichannel coil / receiver channels for parallel imaging algorithms. Multiple electrically automated RF coils [7] (each with an RF chain) of MIMO [8], [9] are digitized with a very high precision digitize. An Optimized implementation of a MIMO system with on chip quadrature signals processing is done on the K-Space raw data to obtain the clinical images.Results

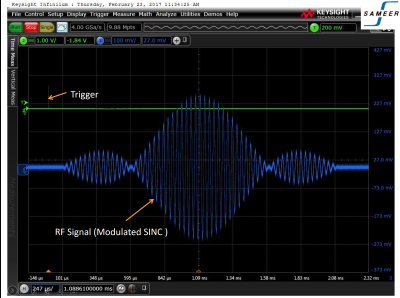

The SoC approach of MRI spectrometer is developed and integrated with the Indian MRI system. Figure 4 shows one of the images of a fruit scan performed. In this developed approach the data processing relies heavily on the pulse sequence format in transmitter and FFT transforms of the acquired data [10]. The developed system interface helps in automatic calibration of MRI Scanners related to Larmor frequency approach, generation of pulse amplitude modulation, design implementation for any waveform with programmable width and arbitrary shape required for clinical anatomical sequences to select multi slices of the human anatomy, generate selective pulse sequences to distinguish fat or water, generate waveforms for perfect image localisation, generation of three axis gradient waveforms , pre-scan analysis, , Automatic RF power gain adjustments, flip angle calibration, Transmitter and receiver isolation, free induction decay analysis are some of the other features which are mandatory for accurate spatial and temporal requirements.Conclusion

The implemented System on chip (SoC) MRI spectrometer design is based on a 28 nanometer, single chip approach. An SoC, comprising of multi-layered processor and programmable FPGA architectural layers. This has helped to design and provide a highly customized, lower powered, higher memory storage, smaller board size, with huge digital signal processing slices. The design and development MRI spectrometer is numerically programmable and up-gradable to various Tesla field scanners at a very minimal costs. Performance evaluation of the system results in much faster and hassle free parallel imaging algorithms in much lesser time duration.Acknowledgements

The author hereby acknowledges the support extended by MeitY,Government of India, for providing the financial support to carry out research and development of Indigenous Indian MRI project.References

[1]. Goetz, C., P. Choquet, J. Hyacinthe, and A. Constantinesco. "Low cost NMR/MRI spectrometer using industrial boards." In Kyoto, Japan:(ISMRM, 12th Scientific Meeting t Exhibition), vol. 2, p. 628. 2004.

[2]. Su, Yushan, Michael Anderson, Jonathan I. Tamir, Michael Lustig, and Kai Li. "Compressed sensing MRI reconstruction on Intel HARPv2." In 2019 IEEE 27th Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM), pp. 254-257. IEEE, 2019.

[3]. Li, Limin, and Alice M. Wyrwicz. "Design of an MR image processing module on an FPGA chip." Journal of Magnetic Resonance 255 (2015): 51-58.

[4]. Meyer-Baese, Uwe, and U. Meyer-Baese. Digital signal processing with field programmable gate arrays. Vol. 65. Berlin: springer, 2007.

[5]. Jiang, Jiantong, Zeke Wang, Xue Liu, Juan Gómez-Luna, Nan Guan, Qingxu Deng, Wei Zhang, and Onur Mutlu. "Boyi: A systematic framework for automatically deciding the right execution model of OpenCL applications on FPGAs." In Proceedings of the 2020 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays, pp. 299-309. 2020.

[6]. McFarland, Michael C., Alice C. Parker, and Raul Camposano. "The high-level synthesis of digital systems." Proceedings of the IEEE 78, no. 2 (1990): 301-318.

[7]. Sohn, Sung-Min, Lance DelaBarre, Anand Gopinath, and John Thomas Vaughan. "Design of an electrically automated RF transceiver head coil in MRI." IEEE transactions on biomedical circuits and systems 9, no. 5 (2014): 725-732.

[8]. Sutar, Najneen. "Methods of Re-Configurable front end for MIMO Architecture for Wireless Systems." Methods 2, no. 11 (2013).

[9]. Jeoong S. Park, Hong-Jip Jung and Viktor K. Prasanna “Efficient FPGA-based Implementations of the MIMO-OFDM Physical Layer”, IEEE Transactions on Communications, vol. 32, no. 18, pp. 571-577, August 2003.

[10]. Chen, Ren, Hoang Le, and Viktor K. Prasanna. "Energy efficient parameterized FFT architecture." In 2013 23rd International Conference on Field Programmable Logic and Applications, pp. 1-7. IEEE, 2013.