4274

Test Bed for High Speed Serial Wireless MRI Data Studies1Victoria University of Wellington, Wellington, New Zealand, 2GE Healthcare, Aurora, OH, United States, 3Stanford University, Stanford, CA, United States, 4Radiology, Stanford University, Stanford, CA, United States, 5Electrical Engineering, Stanford University, Stanford, CA, United States

Synopsis

We developed a test system to perform pseudo-random binary sequence (PRBS) generation and clock/data recovery to assess high speed serial link performance of wireless and optical signal integrity for MRI data interfacing. We demonstrate applications using up to 1Gbps signal rates and show impairments for wireless amplitude shift keyed data transmission, as well as plastic fiber optical interfacing.

Introduction

An emerging area in MRI engineering is the development of new interfacing technologies [1-3] for RF receive arrays, with the goal to overcome some of the historical limits of bulky cable interfacing and balun heating. Wireless MRI data transfer is particularly challenging because present wireless standards address multi-user and mobile networking, while the MRI data transfer region is fixed to the body coil volume in a shielded environment. In the quest to develop custom high speed optical or wireless MRI data links, many development tools are needed to allow rapid iteration of prototypes. Here, we present a testing system that generates high speed pseudo random binary sequences (PRBS) to allow the evaluation of high speed short range serial data transfer for MRI connectivity development.Methods

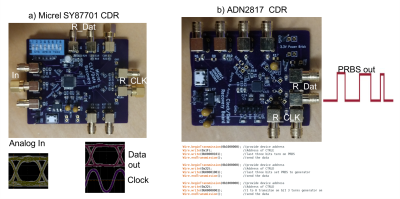

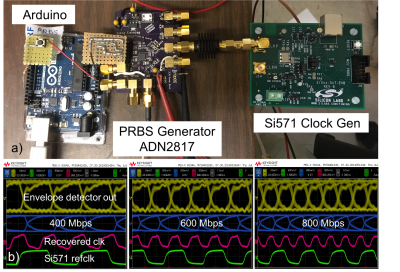

We based our test-bed on clock and data recovery (CDR) integrated circuits. First, we prototyped two CDR boards, based upon the Micrel SY87701 (Fig. 1a) and Analog Devices ADN2817 (Fig. 1b). These support maximum clock/data recovery rates of 1.3Gbps and 2.7Gbps respectively. The ADN2817 includes optional programming as a PRBS data generator, which we exploit. To make a full test system (Figure 2a), an Arduino module provided the configuration programming to the ADN2817, and an Si571 programmable clock generator eval board was the source of the bit rate clock timing. In these tests, we used the SY87701 for clock/data recovery. However this part requires a reference clock to aid the internal phase-locked loop (PLL). This function was provided by a second Si571 clock or by a function generator.Various applications of the test-bed utility were demonstrated for 1) ADL6012 envelope detector bandwidth, 2) dipole antenna transmission of amplitude shift keyed (ASK) data, 3) Firecomms optical transceiver performance, and 4) to demonstrate spectral adjacent channel interference with increasing bit rates.

Results

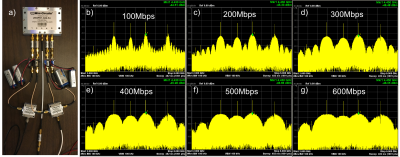

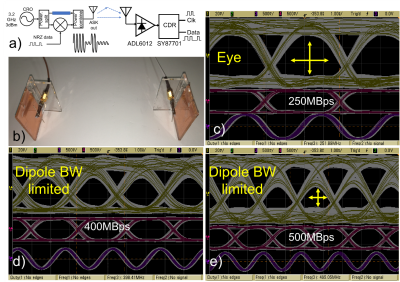

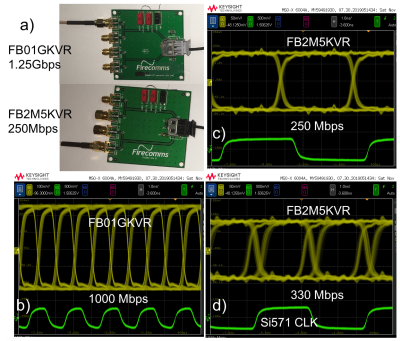

The basic end-to-end functionality is demonstrated in Fig. 2b where a 3.2GHz ASK modulated signal is envelope detected, for rates from 400Mbps to 800Mbps with subsequent clock/data recovery. In Figure 3, this is expanded to show dipole antenna bandwidth limits on the signal integrity. We see that as PRBS bit rates increase from 250 to 500 Mbps, the analog eye pattern becomes progressively closed. At some point this will cause bit errors, though CDR was successful here. In Fig. 4, the PRBS test system is used to toggle FIrecomms optical transceivers. Present day 250 Mbps devices begin to fail beyond 300Mbps PRBS data rates (Fig. 4c,d). For some time, a 1.25Gbps RCLED transceiver was also available and Fig. 4b shows the ease with which it handles 1Gbps PRBS data. Finally, more recent versions of ASK modulators were power combined (Fig. 5a) to demonstrate spectral bandwidth with data rates. Here, four modulated sources with carriers ranging from about 3 to 5.3 GHz, show the classic SINC-like lobes as PRBS rates increase from 100Mbps to 600Mbps using the ADN2817 PRBS generator. The adjacent channel interference increases with bit rate.Discussion

One of the difficulties in developing data links for MRI, is the need for low-cost test components to avoid expensive instrumentation costs. Fortunately, because of the abundance of optical networking products, CDR devices are adaptable and integrate useful test features that are relevant to the MRI wireless and optical interfacing challenges. The application examples of Figures 2-5 demonstrate their flexibility and aid in debugging various signal integrity problems for high speed serial wireless/optical links. There is, however, one major caveat. As CDR and serializer/deserializer (SERDES) functionality becomes a standard feature of FPGAs, these older (and slower!) CDR product families (in particular the ADN28xx series) may be near end of life. The devices we used are particularly useful since they allow any frequency of locking as opposed to CDR components that only support fixed optical (eg SONET/SDH) rates.Conclusions

We prototyped a test system that could generate pseudo-random binary sequence (PRBS) data at rates to 1Gbps for the purpose of testing high speed serial interfacing options such as wireless and plastic optical fiber for MRI. The test-bench included clock and data recovery functionality. The components are low-cost but proved valuable for exploring wireless and optical link signal integrity for future MRI data links.Acknowledgements

The authors would like to thank GE Healthcare for research support, and received funding from NIH grants R01EB019241, U01EB029427.References

[1] A Millimeter-Wave Digital Link for Wireless MRI, K. Aggarwal et al, IEEE TMI, 36, p574, Feb 2017.

[2] BPSK/ASK Wireless Link Assessment for MRI, G. Scott et al, Proc 28th ISMRM p759, 2020.

[3] Perspectives in Wireless Radio Frequency Coil Development for Magnetic Resonance Imaging, L. Nova et al, Front. Phys. Vol 8 Art 11, Feb 2020.

Figures

Figure 4: Firecomms RCLED optical transceiver rate testing. a) Firecomms 1.25Gbps module (no longer available) and 250Mbps transceiver. b) Loopback test at 1Gbps of the 1.25Gbps module using our PRBS generator. c&d) Loopback test of the 250Mbps transceiver with PRBS test rates of 250Mbps and 330Mbps. We see the signal integrity drops rapidly beyond 250Mbps.