1264

An Open-Source Multichannel MRI Console1School of Engineering and Computer Science, Victoria University of Wellington, Wellington, New Zealand, 2Robinson Research Institute, Victoria University of Wellington, Wellington, New Zealand

Synopsis

This abstracts describes the development of a complete multi-channel MRI console that can be the basis for many MR projects. To support the growing open-source hardware MR community we are making a collection of PXIe modules and IP available to anyone to use and develop applications on. A System Controller Board, a 2-channel Tx and 4-channel Rx transceiver board, an FMC General Purpose Module, PXIe data transfer engine IP, Linux API and device drivers can be accessed online https://github.com/mr-kit/.

Introduction

MRI console development is often impeded by high-speed requirements and complexity. We believe that Peripheral eXtensions for Instrumentation express (PXIe) standard can provide a good foundation as it provides significant data bandwidth and synchronisation capabilities. However, PXIe chassis and modules are usually expensive and contain proprietary Intellectual Property (IP). System developers have no choice but to purchase a complete vendor platform or if developing own hardware are still required to pay for IP. This, as well as the system complexity, is a potential barrier to a lot of university-based researchers who want to develop their own instrumentation hardware. Here we demonstrate the development of a complete multi-channel MRI console that can be the basis for many MR projects. To support the growing open-source hardware MR community we are making available a collection of PXIe modules and IP consisting of:- PXIe System Controller Board based on Zynq PicoZed SoC FPGA Module

- A 2-channel Tx and 4-channel Rx transceiver board based on TE0712 FPGA Module.

- An FMC General Purpose Module.

- PXIe data transfer engine IP and Linux API and device driver.

PXIe Implementation

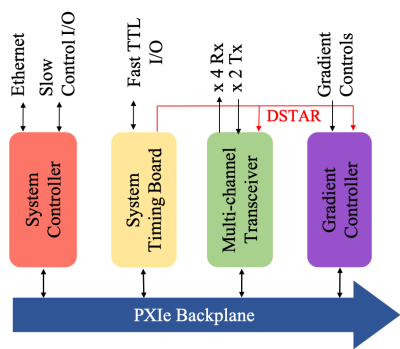

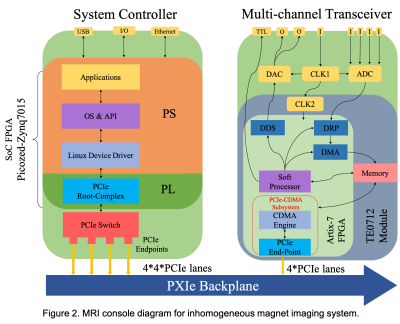

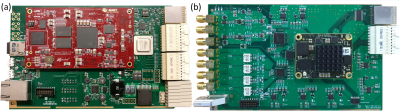

A PXIe system is typically composed of several modules: system controller board, system timing board and a few peripheral boards that provide specific functionality (Figure 1). The system controller board provides a user interface through an operating system (OS), allowing control of any peripheral boards. The synchronisation between multiple boards is carried out by a system timing board. Field Programmable Gate Array (FPGA) devices and the availability of open-source Linux operating systems made it convenient to develop an open PXIe platform. To overcome the proprietary IP associated with PXIe we developed our own open IP solution [1]. We constructed a general-purpose PXIe system controller board, a rapid prototyping peripheral board, and RF transceiver and gradient controller boards. Development of the platform consisted of hardware and software components for both system controller and peripheral boards. On each peripheral board, FPGA fabric was used to implement direct memory access (DMA) and programmed input/output (PIO) engine which interfaces with the root complex of the host system controller. In our case, the host system controller was based on the Xilinx Zynq series system-on-chip (SoC). To speed up development an off the shelf PicoZed ZYNQ7015 [2] system-on-module (SoM) was used. A PCIe switch PEX8624 (PLX Technologies) was used to provide 4 banks of 4xPCIe lanes and support all types of PXIe chassis. Figure 3(a) shows the photo of the system controller board. The management of data transfer between the host and an endpoint was provided by a device driver for the host operating system. An API layer was developed to provide a simple method of performing I/O transactions between the host and the endpoint fabric of each peripheral board. DMA data transfer rates exceeding 100 megabytes per second were successfully demonstrated.MRI System Architecture

The solution to develop an MRI console utilises the open PXIe ecosystem (Figure 2). The host system controller initiates the transfers of pulse sequences, commands, data, to and from DMA memory and pulse sequence engines on each peripheral module. Each peripheral module uses an FPGA with a softcore processor and custom logic to realize specific capabilities.A multi-channel transceiver uses as TE0712 Artix-7 FPGA module (Trenz) [3], with a PCIe-CDMA subsystem [4] to provide PCIe interconnect between the memory on the peripheral module and the system controller.

The receiver section was implemented using a 4-channel 125 MSPS ADC (AD9653) and a digital receive processor DRP in the FPGA. The DRP signal processing chain consists of digital mixing to baseband followed by low pass filtering and decimation using a free Xilinx CIC IP block.

A two-channel transmitter is implemented using a dual 500 MSPS DAC (AD9783) and a DDS/arbitrary waveform generator implemented in FPGA fabric. This approach allows more complex waveform excitation and pre-distortion of RF suitable for B0 eddy current compensation and active Q-damping. A 2 channel Tx will enable users to explore parallel transmit (pTx) and B1 encoding methods. Multiple transceiver boards can be utilized at the same time to provide as many channels as required.

Conclusion

We have a general-purpose PXIe platform implemented in house as an MRI console development. The designs and source code are available at https://github.com/mr-kit/, further information can be accessed at http://www.mr-kit.com/.The system presently is being used to implement inhomogenous imaging with a low-field Halbach magnet with multiple receive coils for B1 spatial separation using TRASE [5] technique.

Acknowledgements

Thanks for hard work from Mathew Bourne and Andrew Ang for prior work on this project.

References

[1] Pxisa.org. (2017). PXI Systems Alliance. [online] Available at: http://www.pxisa.org/Default.aspx

[2] Zedboard.org. PicoZed | Zedboard. [online] Available at: http://zedboard.org/product/picozed

[3] GmbH, T. Trenz Electronic. [online] Trenz Electronic. Available at: https://www.trenz-electronic.de/ GmbH, T. Artix-7 200T Micromodule with Xilinx XC7A200T-2C, Size 4 x 5 cm (com.temp.range).

[4] PCI Express Endpoint-DMA Initiator Subsystem. https://www.xilinx.com/support/documentation/application_notes/xapp1171-pcie-central-dma-subsystem.pdf.

[5] Sharp, J. C., King, S. B., Deng, Q., Volotovskyy, V., & Tomanek, B. High‐resolution MRI encoding using radiofrequency phase gradients. NMR in Biomedicine, 26(11), 1602-1607; 2013.

[6] Cooley, C. Z., Stockmann, J. P., Armstrong, B. D., Sarracanie, M., Lev, M. H., Rosen, M. S., & Wald, L. L. Two‐dimensional imaging in a lightweight portable MRI scanner without gradient coils. Magnetic resonance in medicine, 73(2), 872-883; 2015

Figures