1689

Construction of an open PXIe based scalable MRI console1School of Engineering and Computer Science, Victoria University of Wellington, Wellington, New Zealand, 2Robinson Research Institute, Victoria University of Wellington, Wellington, New Zealand

Synopsis

We have developed an open source PXIe platform tailored for MRI console development. The example design has a multichannel RF transceiver, and signal generation for gradient drive.

Purpose

Magnetic resonance imaging (MRI) console instrumentation, generally has a high entry barrier due to high speed requirements and complexity. With PCIe at its core, we believe that Peripheral eXtensions for Instrumentation express (PXIe) instrumentation standard can provide a good solution for the MRI community as it provides significant data bandwidth, and synchronisation capabilities. However, it usually contains proprietary IP. We have developed a modular open source PXIe platform tailored for MRI console development. The example design has a multichannel RF transceiver, and signal generation for gradient drive capabilities.Method and Implementation

A PXIe system is typically composed of several modules: system controller board, system timing board and a few peripheral modules. These are housed in a PXIe chassis. The system controller board provides a user interface through an operating system (OS), allowing control of any modules within the system. Synchronisation between multiple devices is carried out by the system timing board using a star trigger and system reference clock. Peripheral modules provide specific functionality for a wide range of applications e.g. data capture, waveform generators etc...

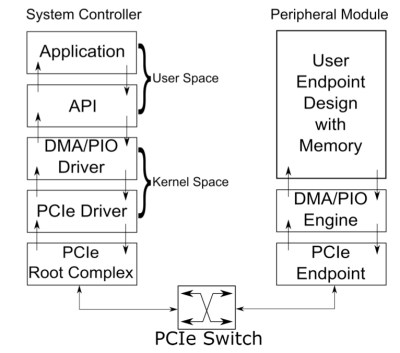

The release of high-performance FPGA devices from vendors such as Xilinx and the availability of open-source Linux operating systems has made it convenient to develop an open PXIe platform. To overcome the proprietary IP associated with PXIe we have developed our own open IP solution1. We have constructed a general-purpose PXIe system control board, a rapid prototyping peripheral board, an RF transceiver and gradient controller modules.Development of the platform consisted of developing the hardware and software components for both system controller and peripheral boards. On each peripheral board, FPGA fabric is used to implement a direct memory access (DMA) and programmed input/output (PIO) engine which interfaces with the root complex of the host system controller. In our case, the host system controller is based on the Xilinx Zynq series system-on-chip (SoC) . The management of data transfer between the host and an endpoint is provided by a device driver for the host operating system (Linux). An API layer was developed to abstract the systems calls between user and kernel space, allowing a simple method of I/O transaction between the host and the endpoint fabric (Figure 1).

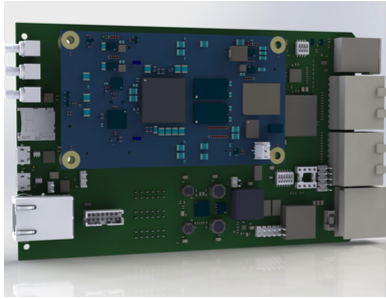

A custom Eurocard sized PXIe system board was developed based on the Avnet Picozed Zynq 7015 module with a 4 lane PCIe root complex (Figure 2)2. The board includes a Broadcom PEX8624 PCIe switch to provide 4x 4 lanes PCIe (Generation 2) to the PXIe backplane. A gigabit ethernet, USB and TTL IO are accessible from the front panel.

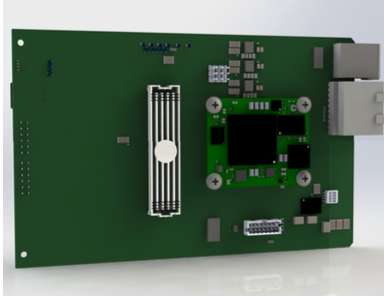

Another Eurocard sized PXIe peripheral board was developed based on the Artix-7 TE0712 module from Trenz Electronics3. The Artix FPGA device is used to host the PCIe endpoint and provide the programmable logic required to support the FPGA mezzanine carrier (FMC) interface and the IO modules connected to it (Figure 3). An example being implementing a digital receiver implemented in the FPGA fabric to process the data from a high-speed ADC FMC module.

Conclusion

We present a functional, open PXIe platform consisting of system controller and FMC peripheral boards. The implementation of the supporting DMA/PIO engine on both the root-complex and endpoints allows fast data transactions to be performed. Keeping user development in mind, we have reduced the software complexity of sending and receiving data to single functions through the API abstraction and reduced hardware complexity by using SoM solutions. The boards presently support 4 lanes at PCIe generation 2 specification (5 GB/s). FMC peripheral modules have been developed to provide RF and gradient system capabilities.Acknowledgements

No acknowledgement found.References

1. M. Bourne, R. Dykstra, S. Obruchkov. "An open source PXIe platform for MRI instrumentation development." Proc. Intl. Soc. Mag. Reson. Med. 25 (2017)

2. “Avnet,” http://zedboard.org/product/picozed, 20173. “Te0712,” https://shop.trenz-electronic.de/en/TE0712-02-200-2C- Micromodule-Artix-7-XC7A200T-2C-4x5cm-standard-footprint-com.- temp.-range?c=341, 2017