2716

Flexible General-Purpose Embedded System for Real-time Feedback and Dynamic B0 Shimming1MPI for Biological Cybernetics, Tuebingen, Germany, 2IMPRS for Cognitive and Systems Neuroscience, Eberhard University of Tuebingen, Tuebingen, Germany, 3Institute of Physics, Ernst-Moritz-Arndt University Greifswald, Greifswald, Germany

Synopsis

B0 shimming methods are becoming more sophisticated. Methods such as multi-coil shimming, dynamic B0 shimming with pre-emphasis and real-time feedback all require additional hardware to drive the shim coils.

In this work, we present a novel general-purpose embedded platform for controlling any of the above mentioned shim systems. Control software can be developed on Linux, while low-level scripts are used for optimal control of hardware interfaces.

Purpose

Develop a universal platform for B0 shimming that is flexible, scalable and has high performance. The platform can be used for multi-coil B0 shimming, dynamic B0 shim updating (DSU) with pre-emphasis and real-time feedback B0 shimming.Introduction

B0 shimming methods are becoming more sophisticated. Methods such as multi-coil shimming1, dynamic B0 shimming with pre-emphasis2,3 and real-time feedback4,5 all require additional hardware to drive the shim coils.

In this work, we present a novel general-purpose embedded platform for controlling any of the above mentioned shim systems. Control software can be developed on Linux, while low-level scripts are used for optimal control of hardware interfaces.

Method

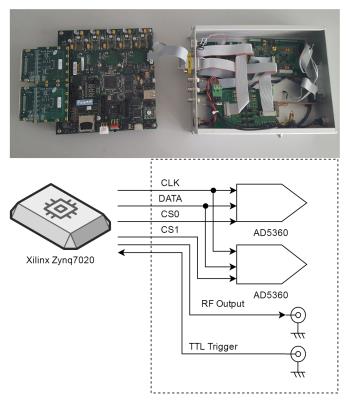

A Xilinx system-on-chip (SOC) Zynq 7020 evaluation board was used for developing the control system. The SOC was chosen because of its integrated field programmable gate array (FPGA) and embedded microprocessor that makes it highly flexible.

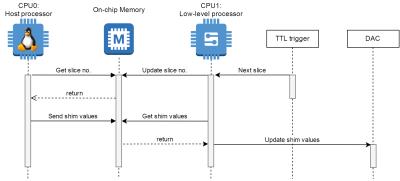

The SOC has two CPUs that can be run asymmetrically: one CPU was used as the host processor while the other was dedicated to low level hardware control. A Linux distribution (PetaLinux) was installed on the host processor. The two processors communicated through data shared memory (the On-Chip memory) as shown in the interaction diagram in Fig. 1.

Registers were implemented in the programmable logic (FPGA) to read/write the gradient values of the MRI host computer (in this case, a Siemens scanner). Communication with the B0 shim amplifiers is done via two 16-channel digital-to-analog converters (DAC) AD5360. The SOC uses a 5MHz serial peripheral interface (SPI) protocol to update the DACs (Fig. 2). Therefore, a total of 32 channels is available and this can be extended in a similar fashion to a larger number of channels (for multi-coil setups of more than 32 loops). This was implemented on the hardware-dedicated processor, CPU1, and thus the update rate is 6us/ch (compared to an update rate of 20us/ch on the Linux system using the spidev.h library).

A TTL external trigger was used to synchronise the MRI sequence with the SOC controller board. The signal is sent directly to the processor as an interrupt and signals that the shim values need to be updated.

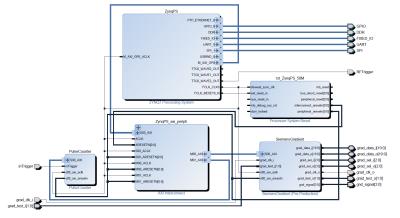

The pulse-width modulation (PWM) module of the SOC is used to generate a train of rectangular pulses. These pulses can be used as excitation pulses for an NMR field camera. The frequency and duty-cycle ratio can be set programmatically. Extra peripherals such as the USB or FPGA pins can be used to read in NMR field camera data for real-time feedback. The hardware implementation of the FPGA can be seen in Fig. 3.

Testing

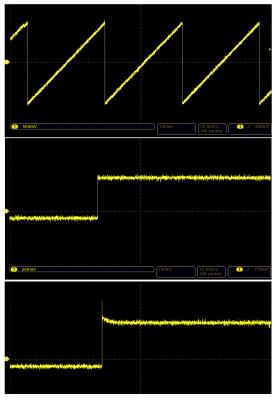

The on-chip communication between processors were tested by generating a signal only on an edge-triggered signal from the TTL input. The generated signals were either: a saw-tooth signal, a rectangular wave or a pre-emphasis signal. This was done to show that arbitrary waveforms could be generated with a very fast update rate (Fig. 4). The output also showed that communication with the DACs were stable and correct.Conclusion

A general purpose B0 shimming platform was developed. It can control up to 32 channels for either multi-coil or spherical harmonic shimming. Arbitrary waveforms can be used for either pre-emphasis or real-time feedback control of the B0 field.Acknowledgements

No acknowledgement found.References

[1] Juchem C et al. JMR 2011.

[2] Edler & Hoult. MRM. 2008.

[3] Fillmer A et al. MRM. 2016.

[4] Duerst Y et. al. MRM 2015.

[5] Wilm B et al. MRM 2014.

Figures