# A Low Cost Signal Modulator for a Field Programmable Gate Array based Parallel Transmit System

Benson Yang<sup>1</sup>, Clare McElcheran<sup>2</sup>, Fred Tam<sup>1</sup>, and Simon Graham<sup>1,2</sup>

<sup>1</sup>Physical Sciences, Sunnybrook Research Institute, Toronto, ON, Canada, <sup>2</sup>Medical Biophysics, The University of Toronto, Toronto, ON, Canada

#### Introduction:

Parallel transmit (PTx) systems are receiving increasing interest in multiple MRI applications such as B1 shimming, patient safety, imaging acceleration and application-specific radio frequency pulse design. However, PTx is still an emerging technology and is not widely available. Optimal system channel count is one area that has not received much attention, but an important factor for commercial adoption. The field-programmable gate array (FPGA) is a mature technology that is commonly used for devices that require high speed

logic and digital computations. Our goals are to design, build and validate a simple, low cost and scalable FPGA-based system that is easily inserted into an existing 3T MRI system.

#### Methods:

Our prototype PTx system (Fig. 1) is designed for 8kW total output power. System control and monitoring are provided by a National Instruments (NI) Labview user interface (UI) and NI FPGA modules for high speed communication (up to 1 Megasample per second) as well as reliable real-time signal modulation. The multi-channel RF inputs (eg. FPGA synthesized) are independently generated and feed into scalable modulators consisting of a Silicon Radio Frequency Integrated Chip Vector Modulator (HPMX-2005, Si-RFIC VM), a low pass filter to remove high order harmonics above the Lamor frequency and a Gallium Arsenide Monolithic Microwave Integrated Circuit Attenuator (MAAVSS0006, GaAs MMIC). We are designing for 4 to 64 channel systems. To reach our output power target, multi-stage power amplifiers are used for our low to mid channel count system whereas a multi-stage integrated circuit approach is used for high channel count system. To keep the system compact, our long term goal is to layout the highlighted modules in Fig. 1 (red dashed lines) onto a single printed circuit board when applicable.

### Results:

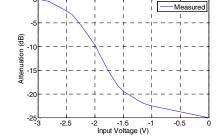

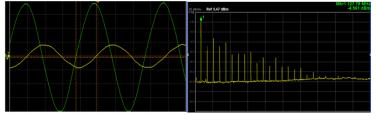

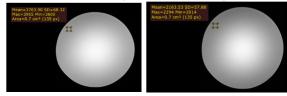

Bench test results are shown for the VM chip in Figs. 2 and 3 and the attenuator chip in Fig. 4. Fig. 2 displays a sample reference signal (yellow) versus the same signal phase shifted by 100 degrees (as marked in orange) at maximum output gain (green). Fig. 3 displays the VM output signal and high order harmonics to be filtered. Fig. 4 shows the full attenuation capabilities of the chip which is driven by a negative voltage bias from 0 to -3V. Lastly, Fig. 5 shows example MR images without and with a single channel of the PTx system inserted into the RF transmission pathway of a 3T system (MR750, GE Healthcare). There is a signal decrease in the image due to the -4dB attenuation but no imaging artifact was present. This result suggests that our single channel prototype module is working as per design.

# Discussion:

The total estimated system costs are highlighted in Table 1. The component costs for the Si-RFIC and GaAs MMIC are \$5 and \$3 per chip, respectively. Our complete VM module assembled and packaged is not expected to exceed \$500 per channel which is considerably less than a complete NI-FPGA with RF transceiver system. There are advantages to using a fully FPGA-based system for our experiments, however the ease of use of NI-RF adapters do not justify the additional cost at present. Alternative FPGA methods can be explored in the future.

## Conclusion and Future Work:

Our FPGA PTx system concept balances flexibility, performance and overall system cost. The signal modulation module has been tested on the bench and during MRI. The next steps are further design and development of the user interface as well as implementation of the FPGA controls for future demonstrations. References:

**Figure 4: Attenuation Chip Profile**

[1] Hewlett Packard: HPMX-2005 Technical Data, [2] M/A-Com: MAAVSS0006 Rev. V1, [3] National Instruments http://www.ni.com, [4] Feng et al., ISMRM 2008.

Figure 1: System Overview

Figure 2: VM Bench Test

**Figure 3: Frequency Spectrum Plot**

| System             | 8ch            | 64ch           |

|--------------------|----------------|----------------|

| FPGA Control + Our | \$14,000.00    | \$142,000.00   |

| modulation module  | (NI-USB-7845R) | (NI PXI-7842R) |

| FPGA Control +     | \$185,000.00   | \$>1,000,000   |

| Modulation         | NI PXIe-7966R  | NI PXIe-7966R  |

|                    | NI 5791 (RF)   | NI 5791 (RF)   |

**Table 1: System Cost Summary**

Figure 5: MR Image (left, Mean=3763) vs MR Image Attenuated (right, Mean=2163)